TANG Shibiao∗, CHENG Jie, LI Shuai. Research on random number chip array schemefor quantum key distribution products[J]. Chinese Journal of Quantum Electronics,2021,38(4):468-476

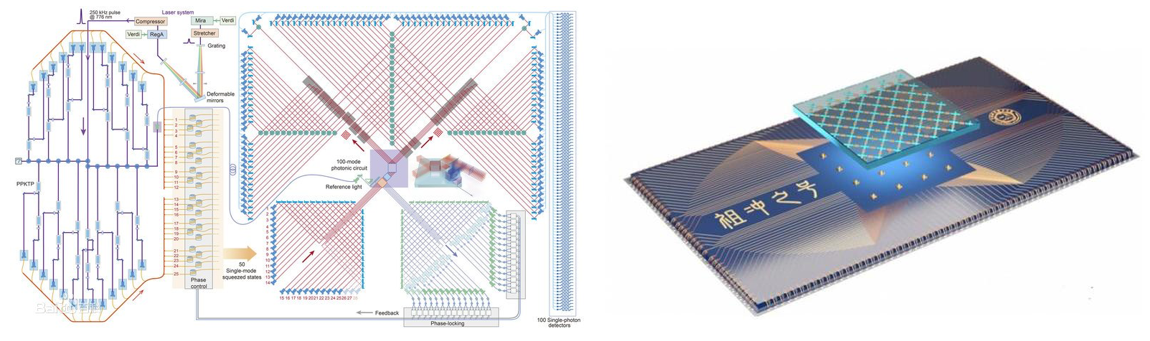

近几年量子信息技术发展迅猛,Google 2019年推出53比特量子计算原型机Sycamore系统,中国科学技术大学团队于2020年和2021年分别成功构建了76个光子、100个模式的高斯玻色取样量子计算原型机 “九章”以及 62 比特可编程超导量子计算原型机“祖冲之号”,后者相较于Google 53量子比特的Sycamore 处理器量子优越性提升 2-3 个数量级,刷新世界纪录。

图1 九章与祖冲之号量子计算机

量子计算机在原理上具有超快的并行计算能力,可望通过特定算法在密码破译方面相比经典计算机实现指数级别的加速。这对当前普遍使用的RSA等经典非对称密码算法构成的潜在威胁逐渐趋于现实。量子信息科技是事关国家信息安全和国防安全的战略性领域,世界各国均对其给予了极大关注,我国于“十四五”规划、国家中长期科技发展规划中均提出要加强量子信息技术的研究投入。

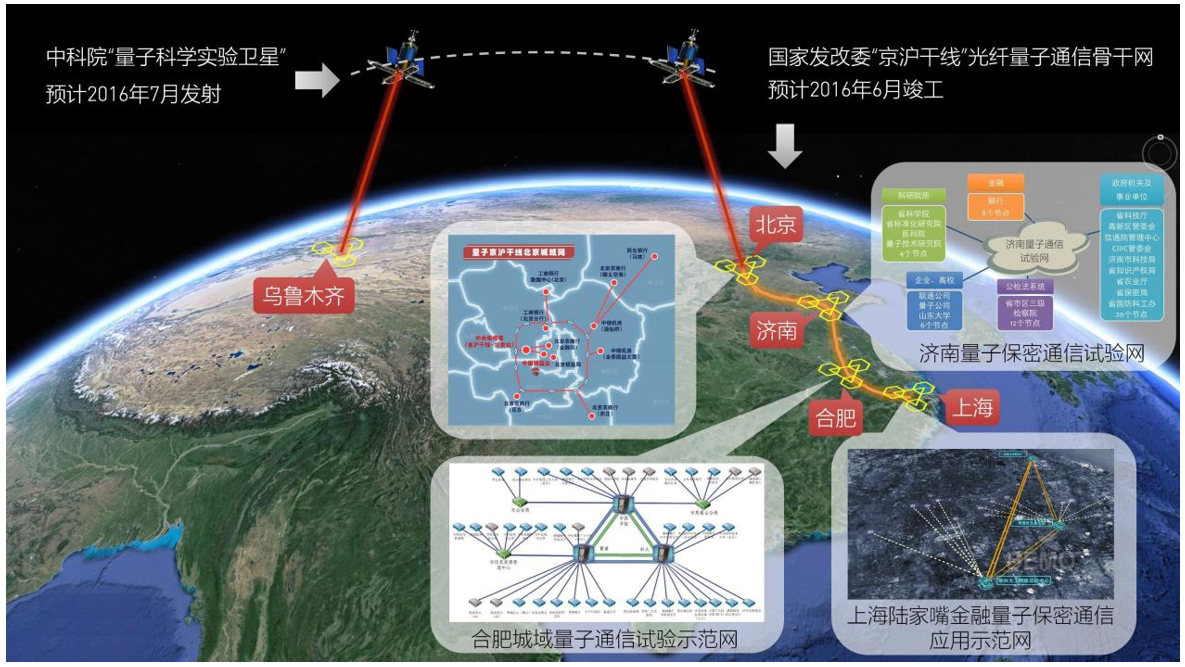

为应对量子计算对经典加密通信领域构成的挑战,作为对抗量子计算威胁的技术路线之一,量子密钥分发技术(Quantum Key Distribution,QKD)的研究也展现出理论与实用化快速并驱发展的特点,在国防、政务、金融、能源等领域具有广泛应用前景,也是我国在量子信息领域发展较为领先的一项技术。经过多年的持续研究探索,目前我国建成了全长2000余公里的全球首个广域量子保密通信技术验证及应用示范项目“量子京沪干线”;“墨子号”量子科学实验实现了星地之间以及7600公里的洲际量子密钥分发。

图2 量子京沪干线及星地量子密钥分发

为服务于新时期下国家信息安全发展需求,QKD作为一种新兴密码技术也正在按照国家相关标准进行快速的科研成果转化。QKD发送端采用随机数进行编码并制备相应的量子态光脉冲,接收端则完成解码和量子信号探测,双方再经过基矢比对、纠错、保密增强等数据处理过程,即可得到一组双方共享的对称密钥;其中,根据安全性分析,上述随机数要求采用物理随机数源产生。根据《GM/T 0028-2014 密码模块安全技术要求》、《GM/T 0062-2018 密码产品随机数检测要求》等标准要求,作为市场化的密码产品应采用核准的随机数源,并按照产品等级要求配备对应的随机数自检算法。为此,科大国盾量子研究团队基于一款核准的随机数芯片WNG-8设计了一种随机数芯片阵列,并设计实现了高速随机数源实时自检方案,保证了QKD产品所用随机数的合规性与可靠性。

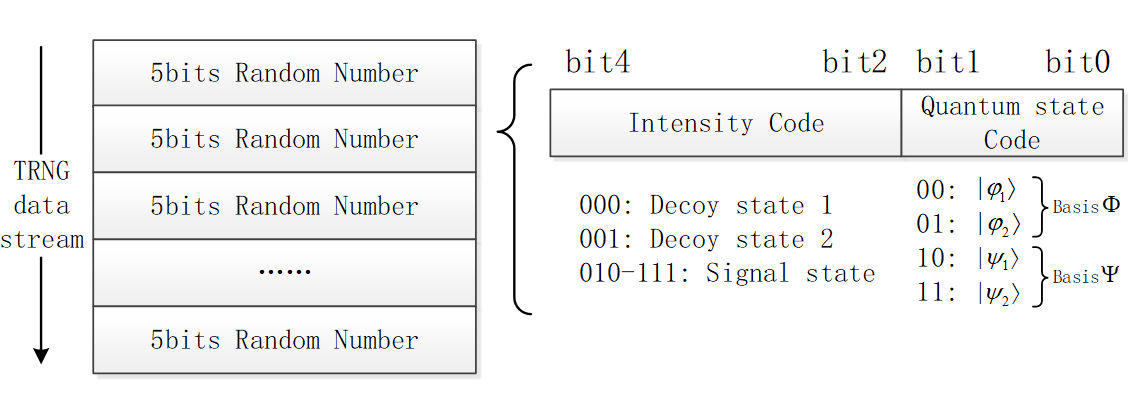

以一款工作频率为80 MHz的偏振编码QKD产品为例,发送端可以使用5 bits的随机数编码一个强度随机的量子态光脉冲信号,因此要求随机数源能提供400 Mbps以上的随机数。在该编码方案中,2 bits用于编码二维希尔伯特空间的四种量子态、、、;3bits用于编码平均光子数为的信号态、平均光子数为的诱骗态1、平均光子数为的诱骗态2,可以使得最终发射的量子态光脉冲信号中信号态:诱骗态1:诱骗态2的比例为6:1:1,且四种量子态、、、的比例为1:1:1:1,该编码方案示意图如下图3所示:

图3 随机数编码量子态方案示意图

WNG-8芯片是一款20Mbps速率的数字物理噪声源,为满足以上80 MHz工作频率QKD产品对随机数的需求,设计采用22片WNG-8芯片组成随机数阵列,FPGA与22片WNG-8随机数芯片的连接关系如下图4所示:

图4 FPGA与WNG-8芯片阵列连接关系

22片WNG-8芯片分成2组,每组11片WNG-8芯片,在FPGA内部将相邻两片随机数芯片输出的20 Mbps数据进行实时异或处理。通过采用该相邻异或设计,可以保证单片WNG-8芯片失效后该阵列输出的随机数质量合格,提升了系统的可靠性。经过以上处理后,22片WNG8芯片能够输出400 Mbps的有效随机数。

根据《GM/T 0062-2018 密码产品随机数检测要求》,需对QKD产品的随机数发生器按照D类产品要求检测,检测项目为《GM/T 0005-2012 随机性检测规范》中规定的扑克检测(检测参数m=2)。扑克检测是将待测的n bits序列按照参数m分成个长度为m bits的子序列,再统计N个子序列中第i种比特序列模式的出现频数。随后计算,再得出随机性度量指标,其中igamc函数为不完全伽马函数。最后,将Pvalue与门限值0.01比较,如果低于该门限值,则扑克检测未通过。

为加快扑克检测的统计速度,本文利用的单调递减特性,通过计算中间量的上限值S,简化扑克检测运算数据量,同时为FPGA实现扑克检测提供便利。

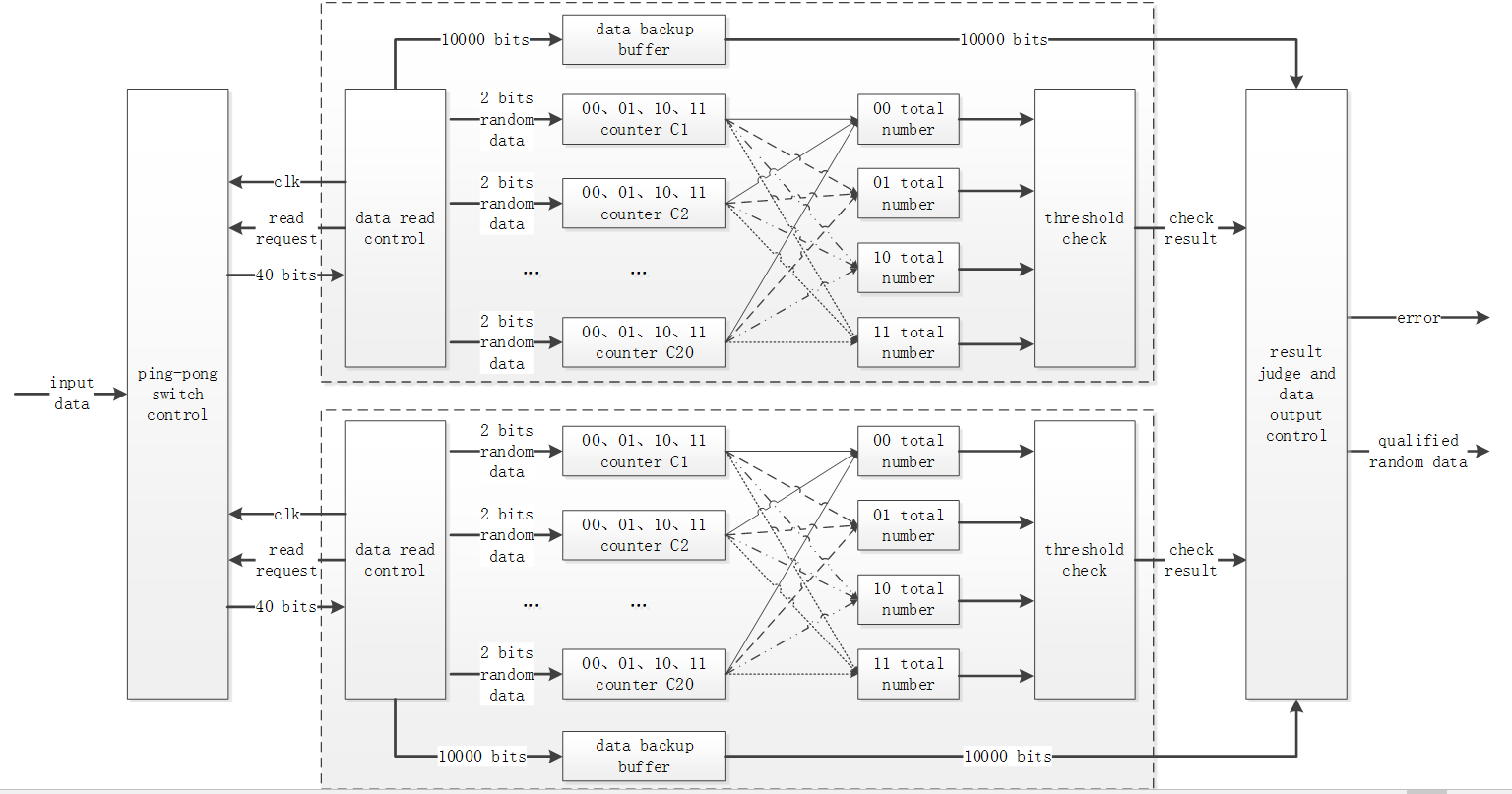

本文中基于FPGA设计实现的扑克检测模块,内含2个10000 bits随机数扑克检测单元,通过乒乓切换的方式提高处理效率,并利用FPGA自身并行计算的优势大大提升检测速率。该扑克检测模块将WNG-8阵列产生的400Mbps随机数数据流按照10000bits自动分割成段,再通过20路00 01 10 11四种比特序列模式的频数统计计数器实现快速统计,统计结果计算并与上限值S对比完成检测。整个扑克检测模块的结构框图如下图5所示:

图5 扑克检测模块框图

对该扑克模块进行仿真及上板实测验证,当FPGA运行频率设计为100 MHz时,总处理带宽达到3.8 Gbps左右,远高于以上80MHz工作频率QKD系统所需的400Mbps扑克检测速率需求。

将该高速扑克检测模块在Altera公司EP3C120 FPGA上编译后显示占用5306个LE逻辑单元,占芯片总逻辑单元的4.5%,编译布局布线后的STA静态时序分析结果显示最大可运行时钟频率fmax达到203.05 MHz。如果有更高的处理带宽需求,完全可以将运行时钟(100 MHz)进一步提升,或者将检测单元数量增加以进一步发挥FPGA的并行处理优势,预计通过以上升级方式可以很快实现10 Gbps随机数源的扑克检测需求,有望支持未来更高系统频率的QKD产品研究工作。

公司介绍:

科大国盾量子技术股份有限公司成立于2009年,由中科大发起组建,主要从事量子保密通信产品的研发、生产、销售及技术服务等,为各类光纤量子保密通信网络以及星地一体广域量子保密通信地面站的建设提供软硬件产品。公司已成为全球少数具有大规模量子保密通信网络设计、供货和部署全能力的企业之一,为政务、金融、电力、国防等关系国计民生的重要行业和领域提供全方位的量子保密通信组网及量子安全应用解决方案。

目前公司产品已经被部署在包括全球首条远距离量子通信干线“京沪干线”在内的量子保密通信骨干网,合肥、济南、武汉、上海张江等地的量子保密通信城域网,以及多个行业的量子保密通信接入网等,为金融、电力、政务、国防等领域客户提供安全服务。